半導体は、組み合わせてトランジスタとして使われていると。

次にご紹介するのは、

「知識ゼロからものづくりを学ぶ 機械設計エンジニアの基礎知識」

から

https://d-engineer.com/electric/denkai.html

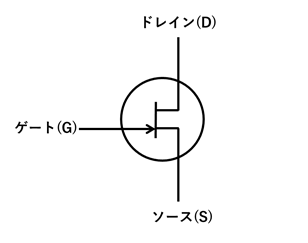

電界効果トランジスタ(FET)

本章では、電界効果トランジスタ(FET:Field Effect Transistor)と呼ばれる素子を紹介します。(以降、電界効果トランジスタをFETと略します。)

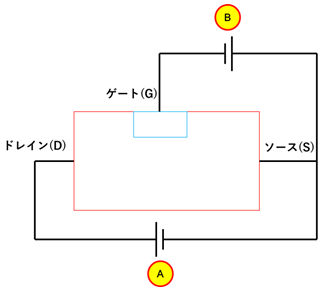

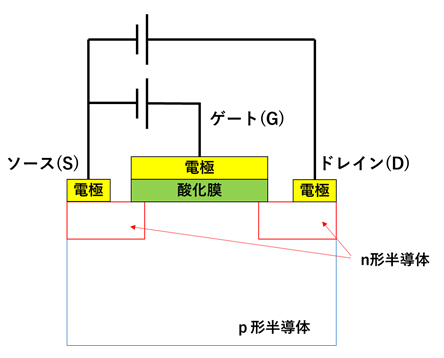

FETはトランジスタと同じように、「ゲート(G)」、「ドレイン(D)」、「ソース(S)」 の3端子が存在します。回路記号は下記となります。

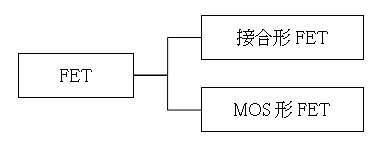

FETの主な特性は、「ゲート部にかかる電圧(ゲート電圧)によってソース・ドレイン間の電流を制御する」 というものです。トランジスタは電流によって制御していましたが、FETは電圧により制御します。また、FETは「接合形」と「MOS形」という2種類に分かれます。(接合形FET・MOS形FET)

それぞれの構造と原理を次に紹介します。

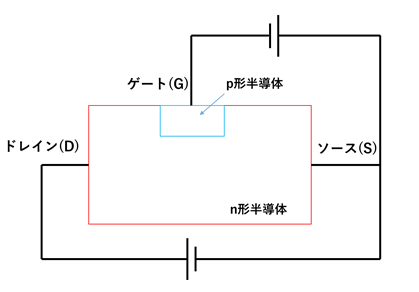

接合形FETについて

■構造

接合形PETの構造と基本回路は下図のようになっています。トランジスタと同様に、p形半導体とn形半導体で構成されておりますが、トランジスタのように層の構造になっておりません。

また、図ではp形半導体がゲート側、n形半導体がソース・ドレイン側につながっておりますが、pとnが反転したものもあります。今回、図で表しているものはnチャネルのFET、反転したものは、pチャネルのFETと呼ばれております。“チャネル”という言葉については後程説明します。

■ 原理

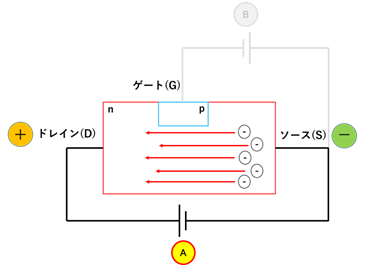

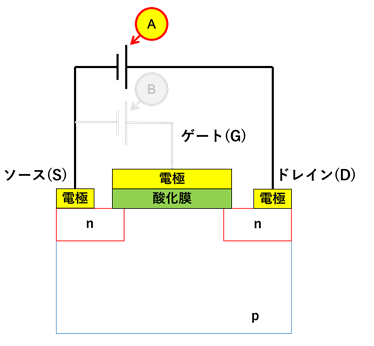

| 基本回路の電源より、FETに電圧をかけた状態を考えてみます。まずFETのソース・ドレイン側に接続された電源(A)を考えます。 |  |

|

ドレイン側にはプラス(+)の電圧、ソース側にはマイナス(-)の電圧がかかるので、n形半導体内の自由電子はドレイン側へと移動します。 |

|

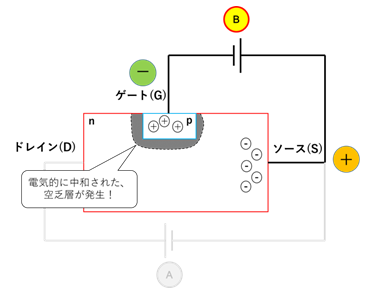

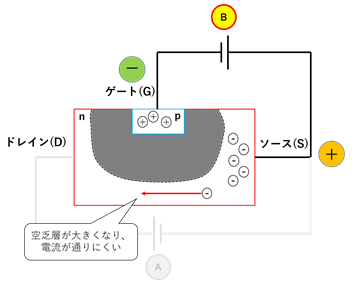

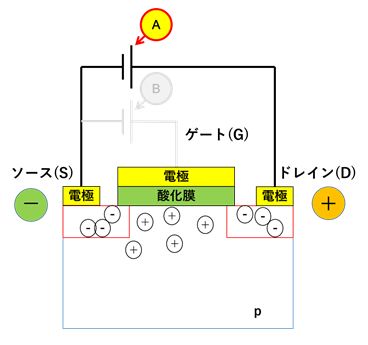

| 次にゲート・ソース間の電源(B)に電圧がかかっている状態を考えてみます。p形半導体にマイナスう(-)の電圧がかかり、正孔はゲート側に引き寄せられます。するとp形半導体とn形半導体の間には空乏層が広がっていきます。 |  |

|

ゲート側にかかる電圧(ゲート電圧Vg)の大きさと共に、空乏層の大きさが変化します。ゲート電圧が大きくなると空乏層も大きくなります。逆も然りです。 |

|

MOS形FETについて

■ 構造

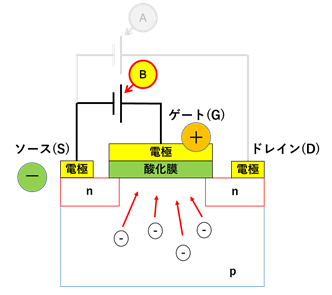

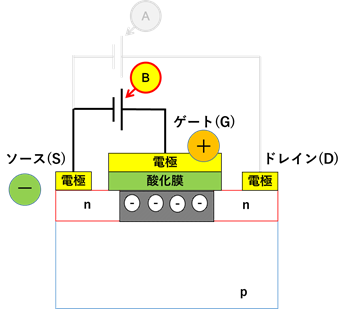

次にMOS形FETについて紹介します。例として、nチャネルのMOS形FETの構造と基本回路を下記に示します。

n形半導体とp形半導体を組み合わせている構造は変わりませんが、絶縁膜という自由電子や正孔の動きをさえぎる層が存在します。

因みにMOSとは「Metal Oxide Semiconductor」の略で、Metalは電極の金属、Oxideは絶縁膜の酸化膜、Semiconductorは半導体を示します。

■ 原理

|

それでは、MOS形FETに電圧をかけた場合の動作を考えてみましょう。 |

|

|

ソース側にマイナス(-)の電圧、ドレイン側にプラス(+)の電圧がかかります。 |

|

|

つぎに、ゲート・ソース間の電圧(B)に対する挙動を考えてみます。 |

|

|

するとn形半導体の間には、自由電子によるチャネルが形成され自由電子が移動できるようになり、ドレイン電流Idが流れることができます。 |

|

以上で、電界効果トランジスタの説明は終わりです。